【A卷】

中華電信股份有限公司96年新進從業人員遴選試題

類別:工務類專業職(四)第一類專員

科目:電子學

\*請填寫入場通知書號碼:

注意:①作答前須檢查試卷與答案卡所標示之卷別(分A、B卷)是否一致,以及入場通知書號碼、桌角 號碼、應試類組是否相符。

- ②本試卷正反兩頁共 50 題,每題 2 分,限用 2B 鉛筆在「答案卡」上作答。

- ③本試卷之試題皆為單選選擇題,請選出最適當答案,答錯不倒扣;未作答者,不予計分。

- ④答案卡務必繳回,未繳回者該科以零分計算。

- 1.若運算放大器為有限增益,則所組成之反向(inverting)組態放大器:

- ①一定具備 virtual short circuit 之特性

②輸入阻抗爲有限值

③電壓增益只與電阻比値有關

④電壓增益也可爲正值

2.下列何者不是理想運算放大器之特性?

①差動(differential)電壓增益=∞

②共模(common-mode)電壓增益=∞

③輸入阻抗=∞

④輸出阻抗=0

3.下列何者不會造成電壓放大器之輸出波形扭曲(distortion)?

①有限頻寬

②輸入阻抗非無限大

③slew rate 限制

④頻率響應之相位非線性

4.由理想運算放大器組成之積分器電路,下列敘述何者錯誤?

①輸出電壓爲負積分結果 ②直流增益無限大

③相位爲 90°

@容易受限於高頻雜訊

5.加一負向電壓於 NMOS 電晶體之 body 端,則:

①門檻電壓(threshold voltage)下降

②通道之等效電阻上升

③通道載子濃度上升

④ 通道下方之空 乏區減少

6.若一 npn BJT 之直流操作狀況爲: $V_{BE}$ =0.7 V, $V_{CE}$ =0.2 V, $I_{B}$ =10 $\mu A$ , $I_{C}$ =1 mA,

則下列結論何者正確?

①  $\beta = 100$

② β ≥100

③ β ≤100

$\oplus$   $\beta = 1000$

7.對於反向器之特性,下列何者錯誤?

①操作之速度受到 propagation delay 影響

② t<sub>PHL</sub>與 t<sub>PLH</sub> 可能不相同 ④ NM<sub>L</sub>=V<sub>IL</sub>-V<sub>OL</sub>

③ NM<sub>H</sub>=V<sub>IH</sub>-V<sub>OH</sub> 8.下列何種類比數位轉換器適合高速應用?

① f- - 1 1- - -1- 4-----

① feed-back type

② dual-slope converter

③ charge-redistribution converter

**4** flash ADC

- 9.有關 MOS 電晶體的通道長度調變(channel length modulation)現象,下列敘述何者錯誤?

- ①通道長度越長此現象越明顯

②通道發生 pinch-off 所造成

③造成電晶體之輸出阻抗降低

⑨電晶體操作於線性區(triode region)時則無此現象

10.對於 emitter follower 放大級之敘述,下列何者錯誤?

①電壓增益<1

②輸出及輸入訊號爲反向

③可當作輸出級使用

④可當作 level shifter 使用

11.有關運算放大器之補償(compensation)技術,何者爲正確作法?

①使 dominant pole 之頻率上升

②使 dominant pole 與 second pole 分開

③增加額外的 high-frequency pole

④使 phase margin 降低

12.有關 NMOS depletion-type 電晶體之敘述,下列何者錯誤?

①門檻電壓(V<sub>t</sub>)>0

② gate 電壓越高,電流越大

③導電之載子以電子爲主

④ body effect 影響門檻電壓

13.若 slew rate 爲  $1 \text{ V/}\mu\text{s}$  之運算放大器當做 unit-gain buffer,輸入之 pulse 高爲 0.2 V,則何者爲 pulse 之最 短寬度,可使輸出達到輸入之電壓最大值?

① 50 ns

② 100 ns

③ 200 ns

**4** 500 ns

14.在一理想二極體與一電阻串接而成的整流器中,若輸入電壓為  $10 \sin \omega t$  伏,則電阻上的直流電壓為若干

伏?

① 1.59

② 3 18

③ 5

**4** 6.36

15.若一尺度常數(scale constant) n=1 的二極體在電流 i=1 毫安時順向壓降 v=0.7 伏,則當 i=0.1 毫安時壓降 急若干伏?

① 0.61

② 0.64

③ 0.74

**4** 0.76

16.在【圖一】的橋式整流電路中,若二次側交流電壓爲弦波 12 伏(rms),二極體順向壓降  $V_D$ =0.7 伏,且 負載電阻 R=100 歐,則負載電壓  $V_o$ 的直流成分  $V_o$  爲若干伏?

① 7.5

② 8.3

3 9.4

**4** 16.3

17.承上題,流經二極體的電流峰值爲若干毫安?

① 85

② 156

3 233

【圖一】

**4** 306

18.若一電壓放大器之輸出電壓在輸出端接上外加的 4.7K 歐負載後即較未接此負載前下降 6%,則此放大器之輸出阻抗爲若干歐?

① 300

② 400

3 500

**4** 600

19.在【圖二】單一電源的 BJT 電路中, $V_{CC}$ =15 伏, $\beta$ =100,

$v_{BE}$ =0.7 伏, $R_I$ =100K 歐, $R_2$ =50K 歐。則在基極上的戴維寧等效電路(Thevenin equivalent circuit)之電壓爲若干伏?

① 5

② 6

3 7

4 8

20.承上題,基極上的戴維寧等效電路之電阻爲若干歐?

① 72.5K

② 50K

③ 33.3*K*

4 22K

21.由理想運算放大器所組成之非反向(non-inverting)組態放大器,下列敘述何者錯誤?

①輸出阻抗為 0 Ω

②輸入阻抗爲無限大

③電壓增益由電阻比值決定

④電壓增益可爲任意之正實數

22.若將 slew rate 為  $1V/\mu s$  之運算放大器接成一 unit-gain buffer,輸入振幅 1V 之弦波訊號,在不失真下最高之輸入頻率爲何?

① 1000000 Hz

② 10000 Hz

00 Hz

③ 159155 Hz

@ 318310 Hz

23.對於運算放大器之 slew rate,下列敘述何者錯誤?

①與電路之頻寬成正比

③受限於電路之直流電流

④爲大訊號操作下之非理想特性

24.下列何者爲 n-type 異質半導體(extrinsic semiconductor)之特性?

①電子爲唯一之導電載子(carrier) ③雜質濃度越高,電洞濃度越低

②穩定狀態下*np > n<sub>i</sub>* ④導電度與溫度無關

②與電容值成反比

25.關於 pn-junction 的敘述,下列何者錯誤?

①內建電壓(building potential)隨掺雜濃度提高而增加

②操作在順向偏壓下空乏區(depletion region)寬度上升 ③內建電壓主要來自於空乏區的電場

④空乏區寬度隨摻雜濃度提高而下降

26.關於 PMOS 電晶體之敘述,何者錯誤? ① source 端的電壓比 drain 端的電壓高

②導電載子以電洞爲主 ④載子由 source 端流向 drain 端

③載子在通道中的運動模式爲擴散(diffusion)

27.下列何種電路只消耗動態功率?

① pseudo NMOS 邏輯 ③ dynamic 邏輯 ② TTL 邏輯 ④ ECL 邏輯

【請接續背面】

| 28          | 右腿          | CMOS   | SRAM   | <b>ウ</b> 鉛流 | , | 下列何者正確? |

|-------------|-------------|--------|--------|-------------|---|---------|

| <b>4</b> 0. | .´  -   1합합 | CIVIOS | DIVAIN | √ /\X ]/  □ | _ |         |

①每一位元只使用 4 個電晶體

②無靜態功率消耗

③儲存之資料不會因爲電源關閉而消失

④爲 ratioless 之電路設計

## 29. 關於濾波器之敘述,下列何者錯誤?

① Butterworth 低通濾波器爲單調下降之頻率響應 ② Chebychev 低通濾波器爲單調下降之頻率響應

③階數由 transfer function 之分母決定

④ transfer function 之係數必需爲實數

30.假設一系統之 transfer function 為

$$H = \frac{a_1 s}{s^2 + (\omega_0/Q)s + \omega_0^2}$$

,下列何者錯誤?

①爲一階系統

②頻率響應爲帶通(band-pass)特性

③低頻增益為0 ④高頻增益為0

①輸入阻抗上升

②輸出阻抗上升

③轉導值 上升

④可視爲一負回授

①電容於 dc 可視爲開路

②雷容於極高頻可視為短路

③電感於 dc 可視爲開路 ④電感於極高頻可視爲開路

①輸入級為雙端輸入單端輸出

②第二級爲單端輸入單端輸出

③電壓增益主要由輸出級提供

34. 關於輸出級之敘述,下列何者錯誤?

① class-A 為線性操作放大器

② class-B 無靜態功率消耗

④ 電路中包括保護電路

③ class-B 的輸出通常爲失真之波形

④ class-AB 可兼顧效率及線性度

【圖三】

35.關於 pseudo NMOS logic 之敘述,下列何者錯誤?

①pull-up 及 pull-down network 皆使用 NMOS 電晶體

②具有靜態功率消耗

③負載(active load)越大,則 Vol.上升

④V<sub>OH</sub>不受負載之大小影響

36.下列何者爲一濾波器之 transfer function?

$$T(s) = \frac{3}{s^2 - 3s + }$$

37.請問 Class-A 放大器之最大輸出效率(efficiency)為:

① 20%

② 25%

③ 33%

**4** 50%

38.在【圖三】的 MOSFET 的電路中,若  $V_{DD}$ =15 伏, $V_{GS}$ =2 伏, 汲極(drain)電壓  $V_D=10$  伏, $R_D=R_S=10K$  歐,則  $R_{GI}$  與  $R_{G2}$  之值

分別應為下列何者?

- ① 8M 歐與 7M 歐

- ② 7M 歐與 8M 歐

- ③ 680K 歐與 470K 歐

- ④ 470K 歐與 680K 歐

39.承上題,則  $I_D$  爲若干毫安?

① 0.2

② 0.4

3 0.5

**4** 0.7

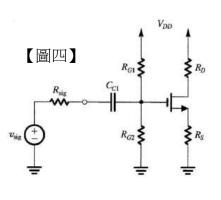

40.在【圖四】的 MOSFET 電路中, 若  $V_{DD}$ =15 伏,

$R_{GI}=6M ext{ is }, R_{G2}=4M ext{ is }, R_D=5K ext{ is }, R_S=2K ext{ is },$

$R_{sig}$ =1K歐, $r_o$ =50K歐, $g_m$ =0.5 毫安/伏, $V_t$ =1 伏,

則就交流小信號  $v_{sig}$ 而言,此放大器的輸入阻抗  $R_{in}$

爲若干歐?

① 999

② 1.98K

③ 2.4M

**4** 4*M*

41.承上題,若汲極上電壓  $v_D$  爲直流電壓  $V_D$  與交流電壓  $v_d$  之和,且  $v_{sig}=0.1$  伏,則  $v_d$  爲若干伏?

① -1 782

2 -2 193

3 -3 864

**4** -4 577

42.承上題,此汲極輸出放大器的交流輸出阻抗  $R_{out}$  爲若干?

① 1 43K

$\bigcirc 2K$

4.56K

【圖五】

① () **②** 1 25 **4** 5

43.承上題,若將  $R_S$  短路且  $I_D$ =2.5 毫安,則  $v_d$  將變爲若干伏?

3 3

44.在【圖五】的理想運算放大器電路中,若  $R_l=2K$  歐,  $R_2$ =68K 歐, $C_2$ =0.01 微法拉(micro-farad),則此放大器轉 移函數的時間常數爲若干毫秒?

- ① 0 02

- 2 0.68

- 3 200

- **4** 680

45.承上題,此放大器轉移函數的波德圖(Bode diagram)在頻率 ω 高於 3dB 點後將以下列何者之速度變化?

- ① -20dB/dec

- ② -10dB/dec

- 3 10dB/dec

@ 20dB/dec

÷

【圖六】

46.在【圖六】的電路中, $V_{DD}$  爲 5 伏, $Q_P$  與  $Q_N$  分別代表

PMOS 與 NMOS 電晶體。若輸入為 A 與 B,輸出為 Y,則此 電路所執行之運算爲下列何者?

- ① AND

- ② OR

- 3 NAND

- **4** NOR

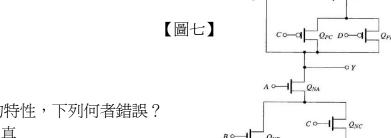

47.在【圖七】的電路中,下列何者正確?

- $\bigcirc$  Y=AB+CD

- $\bigcirc$  Y=AB+CD  $\Im Y = A(B + CD)$

- A Y = A + B + CD

48.有關負回授電路的特性,下列何者錯誤?

- ①可降低非線性失真

- ②可擴展頻寬

- ③可提高增益

- ④可提升輸入阻抗

- 49.有關離散式(discrete)元件組成的電路與積體電路(IC, integrated circuit)比較,下列何者正確?

- ①離散式元件電路可操作於較低的頻率

- ② IC 的體積較大

- ③ IC 各級間通常以電容交連(coupling)

- ④在積體電路內應儘量使用主動元件以節省成本

- 50.有關 CMOS 閘電路中,若Y 爲輸出,則有關上拉電路(PUN, pull up network)與下拉電路(PDN, pull down network)的敘述,下列何者正確?

- ①上拉電路專供非反相輸入之用

- ②上拉電路主要由 NMOS 組成

- ③下拉電路若導通將使輸出爲高電壓

- ④若上拉電路接成並聯則下拉電路將接成串聯